FPGAs can do things that CPUs cannot do as quickly, or as efficiently, or simply cannot do at all.

The bottleneck on rapidly expanding market usage for a powerful FPGA, with hard CPU cores, is that almost all applications use Linux. This requires a lot of memory, most of all RAM, and insufficient built-in RAM means an external DRAM is needed. “Bare metal” usage of the device has been quite challenging.

Until now.

Using Xilinx Zynq FPGA as a microcontroller

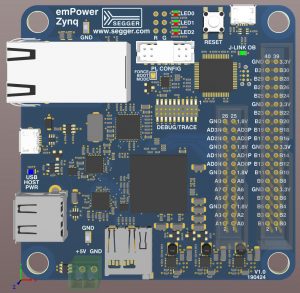

The Xilinx Zynq FPGA with built-in CPU cores (part of the SEGGER emPower Zynq board shown above) has been used in our latest J-Trace PRO for quite some time.

The device has 256 kB of RAM and 512 kB of L2 cache for the two ARM Cortex-A9 CPUs. It also features a built-in 1Gb Ethernet, high-speed USB host and device controllers and many other peripherals. Best of all, any peripheral not included can simply be added using Verilog, VHDL (or similar), i.e. implemented in the FPGA. This device offers so much more power than a simple microcontroller that it is simply a beast!

We wrote a driver and board support package (BSP) for our RTOS (embOS), and some of our middleware (TCP/IP stack (emNet) and USB device stack (emUSB-Device)), all of which are used in the J-Trace PRO. This process enabled us to build a trace probe which is capable of transferring captured trace data in real-time to the host, where it is analyzed and visualized in real time. Streaming the data meant no trace buffer limit, eliminating a significant weakness of less capable trace probes, which is ideal. In this device we do have external memory, but only as an intermediate buffer for the captured trace data. It is not required for the operation of the unit, except for short periods where there is a communication “hiccup”.

Designing emPower Zynq

Using SEGGER tools, the Zynq proved to be so powerful, reliable, flexible and fast that we decided to make our ported middleware and BSP available to the market. We could not find an inexpensive evaluation board without external memory and felt that if this was something we would use, others might too. We wanted a high-speed CPU plus FPGA solution that “simply works”, without requiring external RAM, so, like many times before, we decided to build one ourselves.

Advantages of not using external memory

Eliminating external RAM saves the cost of the RAM, of course. But this also reduces EMI, lowers power consumption, allows for a simpler schematic, a simpler PCB design (with fewer layers), and a smaller PCB. Finally, you also get a faster boot and fewer components mean higher reliability.

The SEGGER emPower Zynq board

The board is in production now and should be available shortly. We plan to make it available at the very reasonable price of 98 Euro ($120 USD).

It features high-speed USB device and host, Gb Ethernet, and an SD Card interface. There is a standard Xilinx connector on the board so that the Xilinx probes can be used for the FPGA. It comes with an on-board J-Link, as well as its own trace connector, for debugging (and tracing) the program running on the Cortex-A9. The CPU boots from a small Quad SPI Flash which contains both the program and the configuration of the FPGA. The FPGA logic is stored in compressed form in the image (using emCompress, which is ideal for the job, reducing the FPGA logic image to a fraction of its original size).

SEGGER will make not only demo software available (easily downloadable via the J-Link OB, which will most likely also get Drag&Drop programming), but will also make this software available for Embedded Studio, our cross-platform IDE.

With SEGGER Software, this powerful device is as simple as a microcontroller!

The entire firmware typically fits into the 512kB L2 Cache. Even if it doesn’t, XIP (execute-in-place) makes it possible to have a program bigger than the cache. This is rarely necessary, but even if it is, it is not a problem. Infrequently used data (such as the configuration of the FPGA logic, web pages, and other constants) can be placed in an area that is not cacheable,

so that the time critical code can continue to reside in the L2 cache.

In our sample projects, the entire project fits easily into the L2 cache, meaning no loads from memory are required once the program is in the cache, and the program executes extremely quickly, on a CPU core specified up to 1GHz. According to Xilinx, a single core delivers 2.5 DMIPS/MHz. We are using just a single core mostly, but dual core versions of “The Beast” are available as well.

The sample projects will be available as usual with the application in source code and can be modified and rebuilt using Embedded Studio. For non-commercial use and for evaluation, Embedded Studio and Embedded Studio PRO can be used free of charge. Embedded Studio PRO comes with all the middleware, including things like IoT tool kit, web and FTP server, and much more.

A Powerful FPGA becomes a Microcontroller

We are quite excited that SEGGER software can turn a powerful FPGA into a microcontroller, opening up a completely new market for the device.

This is certainly a solution to consider for your next project as it has never been easier to harness and use such a powerful device. With SEGGER software, it simply works!

Release of this board and the software is scheduled for early summer. We will keep you posted.